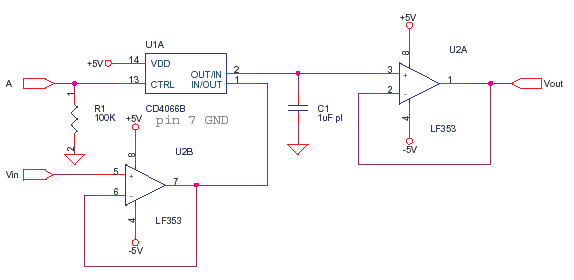

Simple Sample and Hold with CD4066

A sample and hold is like an analog memory. If The digital control A is low 4066 switch is open, and when A is high switch is closed. U2B is a buffer so as to ensure quick charging of C1 thru 4066 on resistance of 100E.

U2A is a FET input opamp buffer which does not load or drain the cap C1. When A goes high the input analog sample is stored in C1. A has to be high for say 10*1uF*100E = 1mS, so that a proper stable sample is stored. When A is low C1 undergoes very slow discharge as opamp input resistance and 4066 off resistance is in giga ohms. The accuracy of reading Vout falls with respect to time due to leakage currents.