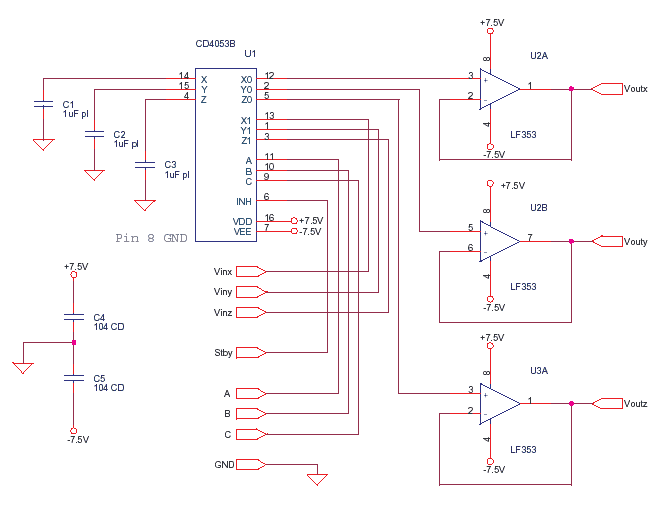

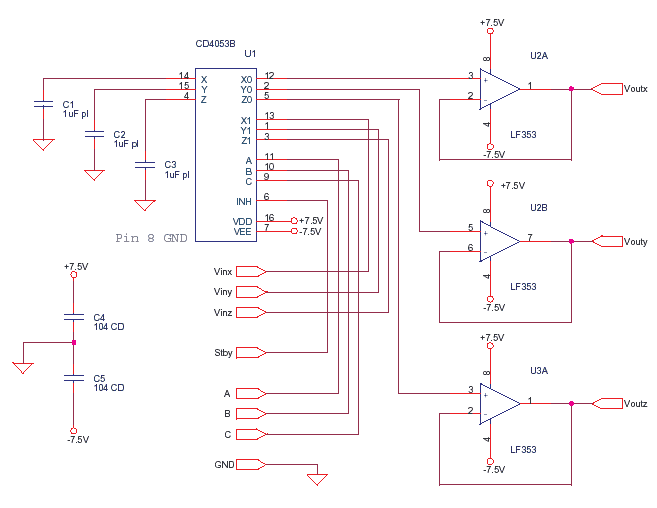

Sample and Hold with Standby CD4053

A, B, and C are the Digital Control for x, y and z input and output pairs.The voltage at Vinx is stored in C1 when A goes high, when A is low the voltage stored in C1 is read by buffer U2A.

It could be used in DMM circuits as Analog Memory DMM range, AC-DC mode, logic control

Another application of Mux 8 Channel 4-20mA Analog Multiplexer

The stby or standby input should be low when sample and hold is operating. If stby is taken high then C1 Cap is isolated and leakage is minimum. The supply of +/- 7.5V is chosen as OFF resistance of 4053 is high at this supply.